实验一四位全加器的设计流程及使用方法

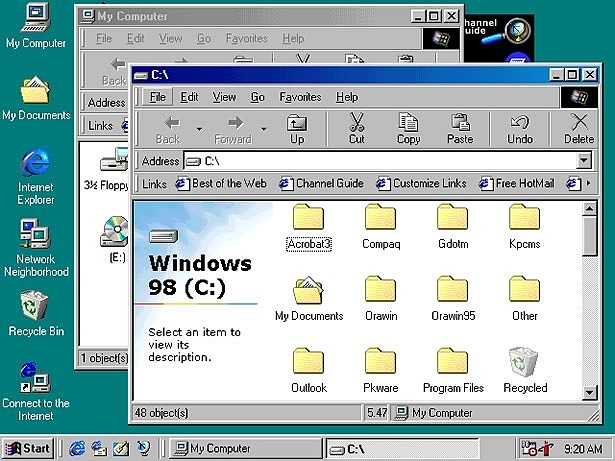

1. 实验一 四位全加器的实现 1. 实验目的 1. 掌握.0图形编辑输入法 2. 掌握环境中文件的编译、仿真和下载方法 3. 了解VHDL语言的设计流程四、掌握环境 如何使用VHDL 二、实验内容 1、用图/原理图的方法实现一个4位全加器。 2、用VHDL语言实现4位全加器,必须使用组件实例化。 3、模拟并通过。 3.下载到实验板并接受。 三、实验步骤 1、图形编辑与4位加法器设计 (1)新建一个图形文件,设计一个1位全加器。 逻辑电路图如下所示(图1-1)。 图 1-1 (2) 实例化所设计的一位全加器并按文件à/à操作

2.文件,完成此操作后四位加法器逻辑图,你会在元件符号表中找到你刚刚制作的一位全加器。 (3) 新建一个图形文件,将四个已经准备好的一位全加器级联成一个四位全加器。 逻辑原理图如图1-2所示。 编辑完成后,保存文件,在文件列表中找到该文件,右键àSet as Top-level,设置为顶级文件,点击编译按钮进行编译。 图1-2 (4)新建一个波形文件,为每个输入端口分配一定的输入信号,保存波形文件,进行功能仿真,观察输出波形与输入信号的关系是否正确。如果是不正确,找到问题并解决; 如果正确,则分配引脚。 赋值完成后,再次编译,使赋值生效。 连接DE2开发板

3.电脑,下载文件到开发板进行验证。 2. 使用VHDL 语言设计4 位加法器 (1) 新建一个VHDL 源文件,文件名为.vhd。 使用VHDL实现1位全加器。 VHDL代码如下:IEEE;USE IEEE..ALL; (A、B、Ci:输入;S、Co:输出);结束; OF (A,B,Ci) n1,n2,n3:;:=A 和 B;n

4. 2:=A 异或 B;n3:=Ci 与 n2;Co

九软件 版权声明:以上发布的内容及图片均来源于网络,如有无意侵犯到您的权利,请联系我们及时删除!