全加器

-

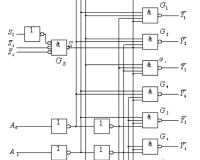

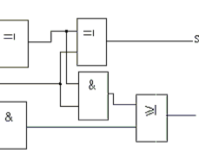

实验一四位全加器的设计流程及使用方法实验内容1、用图形/原理图法实现4位全加器。2、用VHDL语言实现4位全加器,必须使用元件例化。新建图形文件,设计一位全加器,逻辑电路图如下图(图1-1)所示。将设计好的一位全加器进行例化,操作为fileà/à,完成此操...

-

(Day1)全加器实验三实验目的(三)表1全加器真值表8B为四位加法器,其逻辑符号如图2,A3、A2、A1、A0和B3、B2、B1、B0为两个四位二进制数,CI为进位输入端,CO为进位输出端。图2全加器主要用于数值运算,i位全加器可以实现两个i位二进制数的...

-

四位全加器特点及逻辑图、真值表本文主要详解四位全加器,首先介绍了特点及引脚图、真值表,其次介绍了功能表、典型参数及逻辑图,最后介绍了推荐工作条件、电性能以及交流(开关)参数,具体的跟随一起来了解一下。四位全加器特点引脚图及真值表这个改进型的全加器可完成两个...

-

实验三实验目的1.掌握全加器的工作原理与逻辑功能表1全加器真值表8B为四位加法器,其逻辑符号如图2,A3、A2、A1、A0和B3、B2、B1、B0为两个四位二进制数,CI为进位输入端,CO为进位输出端。图2全加器主要用于数值运算,i位全加器可以实现两个i位...